PUBLISHER: Mordor Intelligence | PRODUCT CODE: 1910440

PUBLISHER: Mordor Intelligence | PRODUCT CODE: 1910440

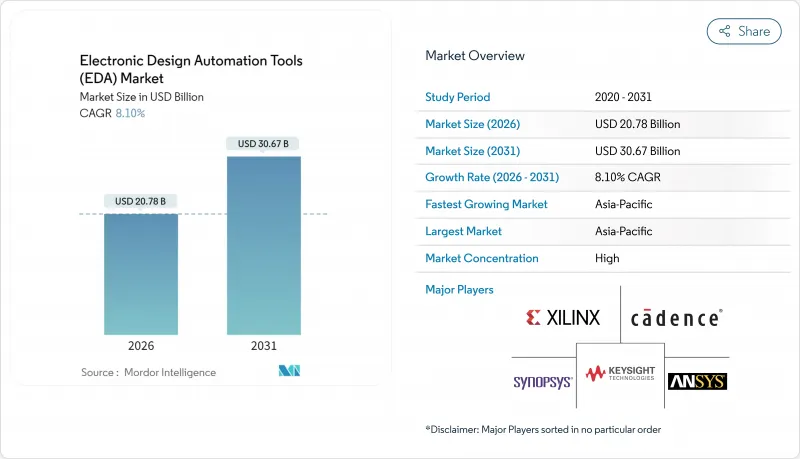

Electronic Design Automation Tools (EDA) - Market Share Analysis, Industry Trends & Statistics, Growth Forecasts (2026 - 2031)

Electronic Design Automation Tools market size in 2026 is estimated at USD 20.78 billion, growing from 2025 value of USD 19.22 billion with 2031 projections showing USD 30.67 billion, growing at 8.1% CAGR over 2026-2031.

The outlook builds on faster transistor scaling, AI-enabled design flows, and closer foundry-tool collaboration. Chip architects are shifting from manual rule tuning to data-driven optimization that shortens tape-out cycles and lowers re-spin risk. Cloud-based capacity bursting is widening access to advanced verification, while automotive functional-safety mandates push formal methods into mainstream design. The 2025 completion of Synopsys' USD 35 billion acquisition of Ansys signals a systemic move toward unified device-to-system platforms able to co-optimize silicon, package, and full-system performance simultaneously. Meanwhile, geopolitical export controls spur parallel EDA ecosystems, compelling vendors to certify flows for multiple regional foundries to avoid revenue erosion.

Global Electronic Design Automation Tools (EDA) Market Trends and Insights

Soaring Chip-Density in Advanced Nodes

Gate-All-Around transistors, backside power delivery, and multi-die packaging produce a ten-fold rise in design-rule checks compared with 7 nm processes. Foundries now co-develop flows with EDA leaders; Synopsys and TSMC certified full digital and analog toolchains for A16 and N2P nodes in April 2025. Unified exploration-to-signoff environments reduce costly re-spins-each exceeding USD 50 million at 3 nm. Intel's 18A program likewise relies on integrated flows for 2.5D/3D architectures that merge compute, memory, and I/O on a single substrate.

Proliferation of AI/ML Accelerators and Custom SoCs

Hyperscale and edge providers increasingly commission purpose-built inference silicon. Cadence posted 40% YoY growth in semiconductor IP revenue in Q1 2025, attributing momentum to AI and chiplet projects. NVIDIA, ASML, TSMC, and Synopsys reported 40X lithography simulation speed-ups through the CuLitho software stack, enabling reticle layouts that meet AI power-per-watt targets. As accelerator heterogeneity rises, SIP reuse and on-package interconnect standards intensify demand for IP verification.

Escalating Licensing Costs for Leading EDA Suites

Annual enterprise bundles for comprehensive 3 nm sign-off now exceed USD 1 million per seat, forcing mid-tier fabs to prioritize tool modules and extend refresh cycles. Oligopolistic supply means price leverage remains with vendors, particularly for timing closure and lithography simulation packages that have no open-source substitute.

Other drivers and restraints analyzed in the detailed report include:

- Rise of Cloud-Native EDA Workflows (EDA-as-a-Service)

- Automotive ISO 26262 Functional-Safety Compliance Needs

- Talent Shortage in Sub-5 nm Physical-Design Engineers

For complete list of drivers and restraints, kindly check the Table Of Contents.

Segment Analysis

Semiconductor Intellectual Property (SIP) posted a 9.7% CAGR forecast, the fastest among tool categories, owing to rising chiplet architectures that favor verified interface blocks and mixed-signal cores. In 2025, SIP accounted for 18.74% of the Electronic Design Automation Tools market revenue, yet its attach rate per project has doubled since 2023 as foundries promote known-good-die strategies. The Electronic Design Automation Tools market size for SIP applications is projected to grow at a significant rate by 2031, underscoring the shift from monolithic SoCs to heterogeneous assembly.

IC Physical Design and Verification retained a 35.82% share thanks to the mandatory nature of placement, routing, static-timing, and DRC in every tape-out. However, AI-enhanced floorplanning automates multi-objective optimization, shrinking turnaround time by 30% on recent 3 nm designs.

Front-End Design tools record a 9.35% CAGR as high-level synthesis (HLS) and natural-language-to-RTL generators improve productivity. The Electronic Design Automation Tools market size for RTL automation is projected to grow significantly by 2031 on the back of AI-assisted code generation that captures functional intent in fewer iterations. Layout, Routing, and Timing Closure still governs 32.10% of the Electronic Design Automation Tools market share, reflecting the irreplaceable nature of sign-off-caliber timing convergence and advanced 3D parasitic extraction.

Generative design platforms now produce placement guidance that reduces wire length by 11% and leakage by 9% versus human scripts. Yet final SOC hand-off still relies on certified timing and electrical-rule reports accepted by foundries, cementing the relevance of established back-end toolchains.

The Electronic Design Automation Tools Report is Segmented by Tool Type (Computer-Aided Engineering, IC Physical Design and Verification, and More), Design-Flow Stage (Front-End Design RTL, and More), Deployment Mode (On-Premise, and Cloud-Based), End-User Industry (Communication Infrastructure, Consumer Electronics, and More), and Geography (North America, and More). The Market Forecasts are Provided in Terms of Value (USD).

Geography Analysis

Asia-Pacific held a 42.05% share in 2025 and advances at a 9.55% CAGR to 2031. Foundry clustering in Taiwan and South Korea anchors regional tool demand, while China accelerates sovereign EDA stacks in response to U.S. export controls. State-backed initiatives channel subsidies toward AI-assisted place-and-route engines and SPICE simulators, aiming to localize flows before 3 nm production ramps. India leverages a large engineering base; design-service firms there grew 17% in 2024 as Western customers sought cost-effective RTL and DFT support.

North America retains influence through leadership in AI algorithms, IP catalogs, and cloud infrastructure. The region's share contracted slightly to 29.15% in 2025, yet remains the primary source of reference tool flows for leading-edge nodes. Export-control regimes require vendors to implement license-key geofencing, adding compliance cost but also locking in North American IP chains. Collaboration between Intel Foundry and Synopsys on 18A certified flows reinforces the U.S. bid to regain advanced manufacturing share. Europe focuses on automotive and industrial applications, with ISO 26262 driving premium verification tool adoption. TSMC's 2025 design center launch in Munich aims to embed foundry engineers within the regional supply chain, providing first-hand support for 3D-IC packaging and power-efficient AI accelerators. The EU Chips Act grants emphasize RandD tax credits for electronic-design clusters, further stimulating regional EDA uptake. Middle East and Africa and South America remain nascent, but showing double-digit growth where government fab projects or IoT rollouts emerge.

- Ansys Inc.

- Cadence Design Systems Inc.

- Synopsys Inc.

- Siemens Digital Industries Software (Mentor Graphics)

- Keysight Technologies Inc.

- Altium Limited

- Zuken Ltd.

- Xilinx Inc. (AMD Adaptive and Embedded Computing Group)

- Aldec Inc.

- Agnisys Inc.

- Lauterbach GmbH

- Silvaco Inc.

- Real Intent Inc.

- Axiomise Ltd.

- Imperas Software Ltd.

- PDF Solutions Inc.

- Flex Logix Technologies Inc.

- Andes Technology Corp.

- Cobham Gaisler AB

- Arteris Inc.

Additional Benefits:

- The market estimate (ME) sheet in Excel format

- 3 months of analyst support

TABLE OF CONTENTS

1 Introduction

- 1.1 Study Assumptions and Market Definition

- 1.2 Scope of the Study

2 Research Methodology

3 Executive Summary

4 Market Landscape

- 4.1 Market Overview

- 4.2 Market Drivers

- 4.2.1 Soaring chip?density in advanced nodes

- 4.2.2 Proliferation of AI/ML accelerators and custom SoCs

- 4.2.3 Rise of cloud?native EDA workflows (EDA-as-a-Service)

- 4.2.4 Automotive ISO 26262 functional-safety compliance needs

- 4.2.5 Growing open-source hardware movement driving verification demand

- 4.2.6 U.S.-China export-control bifurcation accelerating on-shore design flows

- 4.3 Market Restraints

- 4.3.1 Escalating licensing costs for leading EDA suites

- 4.3.2 Talent shortage in sub-5 nm physical-design engineers

- 4.3.3 IP-theft and cyber-intrusion risks in cloud deployments

- 4.3.4 Slower than expected Moore's-Law cadence extensions

- 4.4 Value Chain Analysis

- 4.5 Regulatory Landscape

- 4.6 Technological Outlook

- 4.7 Porter's Five Forces Analysis

- 4.7.1 Bargaining Power of Suppliers

- 4.7.2 Bargaining Power of Buyers

- 4.7.3 Threat of New Entrants

- 4.7.4 Threat of Substitute Products

- 4.7.5 Intensity of Competitive Rivalry

- 4.8 Investment Analysis

- 4.9 Impact of Macroeconomic Factors on the Market

5 Market Size and Growth Forecasts (Value)

- 5.1 By Tool Type

- 5.1.1 Computer-Aided Engineering (CAE)

- 5.1.2 IC Physical Design and Verification

- 5.1.3 PCB and Multi-Chip Module (MCM)

- 5.1.4 Semiconductor Intellectual Property (SIP)

- 5.1.5 Services

- 5.2 By Design-Flow Stage

- 5.2.1 Front-End Design (RTL)

- 5.2.2 Logic Synthesis and Functional Verification

- 5.2.3 Layout, Routing and Timing Closure

- 5.2.4 Sign-off (DFM, Power, SI, Thermal)

- 5.3 By Deployment Mode

- 5.3.1 On-Premise

- 5.3.2 Cloud-Based

- 5.4 By End-User Industry

- 5.4.1 Communication Infrastructure

- 5.4.2 Consumer Electronics

- 5.4.3 Automotive and Mobility

- 5.4.4 Industrial and Energy

- 5.4.5 Aerospace and Defense

- 5.4.6 Medical Devices

- 5.4.7 Other Industries

- 5.5 By Geography

- 5.5.1 North America

- 5.5.1.1 United States

- 5.5.1.2 Canada

- 5.5.1.3 Mexico

- 5.5.2 South America

- 5.5.2.1 Brazil

- 5.5.2.2 Argentina

- 5.5.2.3 Rest of South America

- 5.5.3 Europe

- 5.5.3.1 Germany

- 5.5.3.2 United Kingdom

- 5.5.3.3 France

- 5.5.3.4 Italy

- 5.5.3.5 Rest of Europe

- 5.5.4 Asia-Pacific

- 5.5.4.1 China

- 5.5.4.2 Japan

- 5.5.4.3 South Korea

- 5.5.4.4 India

- 5.5.4.5 Rest of Asia-Pacific

- 5.5.5 Middle East

- 5.5.5.1 Saudi Arabia

- 5.5.5.2 United Arab Emirates

- 5.5.5.3 Rest of Middle East

- 5.5.6 Africa

- 5.5.6.1 South Africa

- 5.5.6.2 Rest of Africa

- 5.5.1 North America

6 Competitive Landscape

- 6.1 Market Concentration

- 6.2 Strategic Moves

- 6.3 Market Share Analysis

- 6.4 Company Profiles (includes Global-level Overview, Market-level Overview, Core Segments, Financials, Strategic Information, Market Rank/Share, Products and Services, Recent Developments)

- 6.4.1 Ansys Inc.

- 6.4.2 Cadence Design Systems Inc.

- 6.4.3 Synopsys Inc.

- 6.4.4 Siemens Digital Industries Software (Mentor Graphics)

- 6.4.5 Keysight Technologies Inc.

- 6.4.6 Altium Limited

- 6.4.7 Zuken Ltd.

- 6.4.8 Xilinx Inc. (AMD Adaptive and Embedded Computing Group)

- 6.4.9 Aldec Inc.

- 6.4.10 Agnisys Inc.

- 6.4.11 Lauterbach GmbH

- 6.4.12 Silvaco Inc.

- 6.4.13 Real Intent Inc.

- 6.4.14 Axiomise Ltd.

- 6.4.15 Imperas Software Ltd.

- 6.4.16 PDF Solutions Inc.

- 6.4.17 Flex Logix Technologies Inc.

- 6.4.18 Andes Technology Corp.

- 6.4.19 Cobham Gaisler AB

- 6.4.20 Arteris Inc.

7 Market Opportunities and Future Outlook

- 7.1 White-space and Unmet-Need Assessment