PUBLISHER: Mordor Intelligence | PRODUCT CODE: 1911415

PUBLISHER: Mordor Intelligence | PRODUCT CODE: 1911415

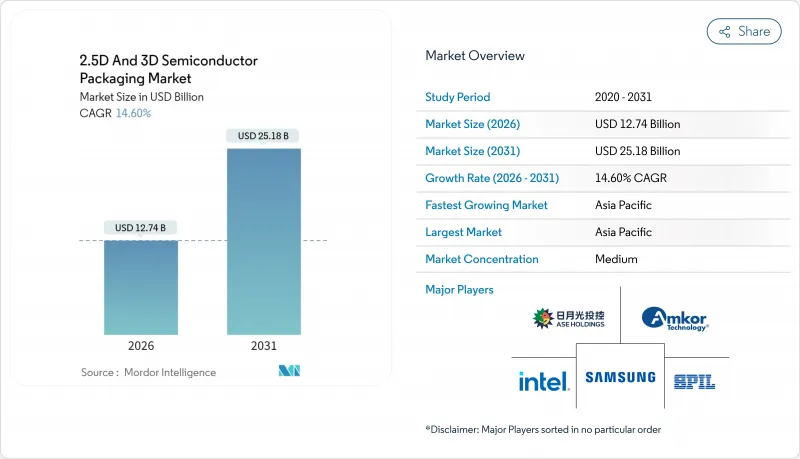

2.5D And 3D Semiconductor Packaging - Market Share Analysis, Industry Trends & Statistics, Growth Forecasts (2026 - 2031)

The 2.5D and 3D semiconductor packaging market is expected to grow from USD 11.12 billion in 2025 to USD 12.74 billion in 2026 and is forecast to reach USD 25.18 billion by 2031 at 14.6% CAGR over 2026-2031.

Driven by AI training clusters that demand terabytes-per-second bandwidth, automotive sensor fusion platforms, and space-constrained mobile devices, the ecosystem is investing in interposer capacity, chiplet standards, and thermally efficient substrates to keep pace. Foundries have moved packaging in-house to secure margins and roadmap control, while OSATs double down on specialty assembly for automotive and photonics use cases. Government subsidies in the United States, Europe, and Asia support regional diversification, yet silicon interposer shortages and cooling limits temper near-term upside. As glass-core substrates, hybrid bonding, and co-packaged optics move toward mass adoption, packaging innovation-not transistor density-will define the next decade of system performance.

Global 2.5D And 3D Semiconductor Packaging Market Trends and Insights

AI/ML Workloads Demanding Ultra-High Memory Bandwidth

Hyperscale training models that now exceed 1 trillion parameters saturate traditional DDR interfaces, prompting GPU vendors to co-package logic with HBM3 stacks delivering 3 TB/s bandwidth-per-socket . Through-silicon vias shorten trace lengths and cut latency, enabling near-memory compute that lowers system power budgets by 15% versus discrete layouts. CoWoS and Foveros platforms position memory and accelerator dies on a shared interposer, a topology that also benefits edge inference devices where form factors prohibit discrete DIMMs. Processing-in-memory prototypes from Samsung and SK Hynix further blur boundaries between logic and storage, reinforcing the 2.5D and 3D semiconductor packaging market as a performance bottleneck eliminator. Data-center operators now tie rack energy efficiency metrics directly to packaged memory bandwidth, converting packaging decisions into capital-expense levers for hyperscale expansions.

Smartphone and Wearable Miniaturization

Premium smartphones integrate more than 50 functions inside system-in-package modules, shrinking board footprint by 40% and cutting z-height below 0.5 mm through fan-out wafer-level packaging . Smartwatches push density further, demanding heterogeneous integration of radios, sensors, and power management in packages under 100 mm2. Stretchable electronics for next-gen wearables add mechanical-strain constraints that organic substrates cannot meet, spurring adoption of warpage-resistant RDL-first fan-out processes. Biocompatible encapsulants and moisture barriers become mandatory as hearables and medical wearables proliferate, enlarging the 2.5D and 3D semiconductor packaging market addressable share within consumer health. Package-level EMI shielding, once optional, is now table stakes for millimeter-wave connectivity and ultra-wideband ranging inside pocket-sized devices.

Escalating CapEx for TSV/Interposer Fabs

Individual CoWoS lines cost 3-4 times standard assembly capacity and push total investment toward USD 10 billion per site . Depreciation periods elongate to 10 years, locking OSATs into high fixed costs that erode price agility. Equipment vendor oligopolies raise tool lead-times beyond 18 months, heightening supply-chain risk. Smaller assemblers, unable to finance TSV etch modules or hybrid-bond aligners, exit the high-end 2.5D and 3D semiconductor packaging market, concentrating power upstream at foundries.

Other drivers and restraints analyzed in the detailed report include:

- Automotive ADAS Electrification Push

- Glass-Core Substrates Entering Volume Trials

- Design-for-Test Complexity and Yield Loss

For complete list of drivers and restraints, kindly check the Table Of Contents.

Segment Analysis

3D TSV solutions captured 43.72% of 2025 revenue, and their 14.85% CAGR keeps them at the forefront of the 2.5D and 3D semiconductor packaging market share race. Samsung's HBM3E stacks supply 1.15 TB/s bandwidth per device, shrinking footprint 60% and cutting board power rails by 30% over planar layouts .

Demand for AI throughput encourages hybrid bonding that eliminates micro-bumps and pushes interconnect pitch below 10 µm. TSMC SoIC samples show 10X interconnect density gains that nearly equal monolithic reticle performance at higher yields. Fan-out wafer-level packaging stays relevant in handsets where thinness outranks TSV, while interposer-based 2.5D bridges dominate chiplet CPUs. Over the forecast, glass-core adoption and backside-power TSVs will blur categorical lines, establishing mixed-mode packages as the de facto high-end configuration, enlarging the overall 2.5D and 3D semiconductor packaging market size.

The 2. 5D and 3D Semiconductor Packaging Market Report is Segmented by Packaging Technology (2. 5D Interposer/FO-SoW, 3D Stacked TSV/Hybrid Bond, and More), End-User Industry (Consumer Electronics, Data Centre and HPC, Communications and Telecom, and More), Application (High-Performance Logic, Memory, RF and Photonics, Mixed-Signal and Sensor Integration), and Geography. The Market Forecasts are Provided in Terms of Value (USD).

Geography Analysis

Asia Pacific commanded 60.05% of 2025 revenue, driven by Taiwan's CoWoS lines and Malaysia's 13% share of global back-end output . Ongoing 15.14% CAGR through 2031 arises from Vietnamese and Thai incentives that add substrate and test capacity.

North America accelerates on the back of CHIPS Act subsidies: Intel's Ohio complex and Amkor's USD 2 billion Arizona plant together raise local throughput by 20% . Defense packaging mandates concentrate secure workloads stateside, and SK Hynix's planned Kansas facility expands HBM-logic assembly near key cloud data-center customers.

Europe focuses on automotive and industrial reliability, with Germany's Silicon Saxony and the Netherlands' photonics clusters receiving Horizon Europe funds. While share lags Asia, EU content rises in high-reliability sectors, lifting the regional 2.5D and 3D semiconductor packaging market size. Emerging regions, South America, the Middle East, and Africa, import fully packaged devices but court investment to localize final test, reflecting a gradual de-risking of globally concentrated supply chains.

- Advanced Semiconductor Engineering Inc.

- Amkor Technology Inc.

- Taiwan Semiconductor Manufacturing Company Limited

- Samsung Electronics Co., Ltd.

- Intel Corporation

- Siliconware Precision Industries Co., Ltd.

- Powertech Technology Inc.

- Jiangsu Changjiang Electronics Technology Co., Ltd.

- GlobalFoundries Inc.

- United Microelectronics Corporation

- Tezzaron Semiconductor Corporation

- STATS ChipPAC Pte. Ltd.

- TongFu Microelectronics Co., Ltd.

- Hana Micron Inc.

- Kulicke and Soffa Industries Inc.

Additional Benefits:

- The market estimate (ME) sheet in Excel format

- 3 months of analyst support

TABLE OF CONTENTS

1 INTRODUCTION

- 1.1 Study Assumptions and Market Definition

- 1.2 Scope of the Study

2 RESEARCH METHODOLOGY

3 EXECUTIVE SUMMARY

4 MARKET LANDSCAPE

- 4.1 Market Overview

- 4.2 Market Drivers

- 4.2.1 AI/ML workloads demanding ultra-high memory bandwidth

- 4.2.2 Smartphone and wearable miniaturisation

- 4.2.3 Automotive ADAS electrification push

- 4.2.4 Glass-core substrates entering volume trials

- 4.2.5 U.S. DoD secure-chip mandates for on-shore 3D-IC OSATs

- 4.2.6 Rapid Uptake of Chiplet Designes

- 4.3 Market Restraints

- 4.3.1 Escalating CapEx for TSV/interposer fabs

- 4.3.2 Design-for-test complexity and yield loss

- 4.3.3 Global interposer silicon-ingot shortage issue

- 4.3.4 Thermal-management and reliability limits

- 4.4 Industry Value-Chain Analysis

- 4.5 Regulatory Landscape

- 4.6 Technological Outlook

- 4.7 Porters Five Forces Analysis

- 4.7.1 Bargaining Power of Suppliers

- 4.7.2 Bargaining Power of Buyers

- 4.7.3 Threat of New Entrants

- 4.7.4 Threat of Substitutes

- 4.7.5 Intensity of Competitive Rivalry

5 MARKET SIZE AND GROWTH FORECASTS (VALUE)

- 5.1 By Packaging Technology

- 5.1.1 2.5D Interposer / FO-SoW (includes CoWoS, EMIB, InFO-SoW, other interposer/fan-out-on-substrate)

- 5.1.2 3D Stacked (TSV / hybrid bond) (includes SoIC, Foveros, stacked DRAM like HBM)

- 5.1.3 Wafer-Level CSP

- 5.2 By End-User Industry

- 5.2.1 Consumer Electronics

- 5.2.2 Data Centre and HPC

- 5.2.3 Communications and Telecom

- 5.2.4 Automotive and ADAS

- 5.2.5 Medical Devices

- 5.2.6 Industrial and IoT

- 5.2.7 Other End-user Industries

- 5.3 By Application

- 5.3.1 High-Performance Logic(CPUs, GPUs, AI accelerators, ASICs, FPGAs)

- 5.3.2 Memory (HBM, DRAM stacks, 3D NAND)

- 5.3.3 RF and Photonics

- 5.3.4 Mixed-Signal and Sensor Integration (ADC/DAC mixed-signal ICs, MEMS sensors, sensor-hub packages)

- 5.4 By Geography

- 5.4.1 North America

- 5.4.1.1 United States

- 5.4.1.2 Canada

- 5.4.1.3 Mexico

- 5.4.2 Europe

- 5.4.2.1 Germany

- 5.4.2.2 France

- 5.4.2.3 United Kingdom

- 5.4.2.4 Italy

- 5.4.2.5 Rest of Europe

- 5.4.3 Asia Pacific

- 5.4.3.1 China

- 5.4.3.2 Japan

- 5.4.3.3 South Korea

- 5.4.3.4 India

- 5.4.3.5 Rest of Asia Pacific

- 5.4.4 South America

- 5.4.4.1 Brazil

- 5.4.4.2 Argentina

- 5.4.4.3 Rest of South America

- 5.4.5 Middle East

- 5.4.5.1 Israel

- 5.4.5.2 Saudi Arabia

- 5.4.5.3 United Arab Emirates

- 5.4.5.4 Rest of Middle East

- 5.4.6 Africa

- 5.4.6.1 South Africa

- 5.4.6.2 Egypt

- 5.4.6.3 Rest of Africa

- 5.4.1 North America

6 COMPETITIVE LANDSCAPE

- 6.1 Market Concentration

- 6.2 Strategic Moves

- 6.3 Vendor Positioning Analysis

- 6.4 Company Profiles (includes Global level Overview, Market level overview, Core Segments, Financials as available, Strategic Information, Products and Services, and Recent Developments)

- 6.4.1 Advanced Semiconductor Engineering Inc.

- 6.4.2 Amkor Technology Inc.

- 6.4.3 Taiwan Semiconductor Manufacturing Company Limited

- 6.4.4 Samsung Electronics Co., Ltd.

- 6.4.5 Intel Corporation

- 6.4.6 Siliconware Precision Industries Co., Ltd.

- 6.4.7 Powertech Technology Inc.

- 6.4.8 Jiangsu Changjiang Electronics Technology Co., Ltd.

- 6.4.9 GlobalFoundries Inc.

- 6.4.10 United Microelectronics Corporation

- 6.4.11 Tezzaron Semiconductor Corporation

- 6.4.12 STATS ChipPAC Pte. Ltd.

- 6.4.13 TongFu Microelectronics Co., Ltd.

- 6.4.14 Hana Micron Inc.

- 6.4.15 Kulicke and Soffa Industries Inc.

7 MARKET OPPORTUNITIES AND FUTURE OUTLOOK

- 7.1 White-space and Unmet-Need Assessment