PUBLISHER: Mordor Intelligence | PRODUCT CODE: 1911823

PUBLISHER: Mordor Intelligence | PRODUCT CODE: 1911823

RISC-V Tech - Market Share Analysis, Industry Trends & Statistics, Growth Forecasts (2026 - 2031)

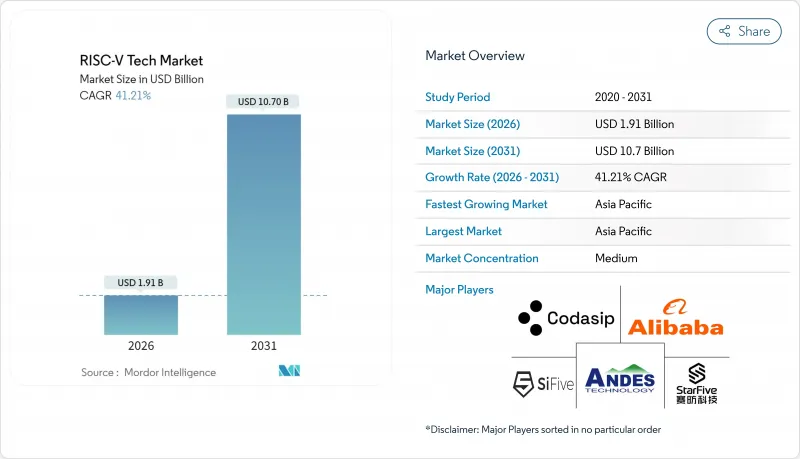

The RISC-V Tech market was valued at USD 1.35 billion in 2025 and estimated to grow from USD 1.91 billion in 2026 to reach USD 10.7 billion by 2031, at a CAGR of 41.21% during the forecast period (2026-2031).

Growth is powered by Asia-Pacific's 45.8% 2024 leadership and its projected 65.2% CAGR, the 64-bit core's 42.4% 2024 domination, and accelerating adoption in consumer electronics, automotive, IoT, and data-center segments. Customizable open-standard IP, sovereign semiconductor programs in the United States, European Union, and China, and an expanding verification ecosystem are amplifying design wins, shortening time-to-market, and attracting new entrants to the RISC-V Tech market.However, software complexity from fragmented ISA extensions, limited backward compatibility compared with ARM, and a shortage of senior EDA talent in mature nodes remain substantial headwinds that could temper adoption momentum.

Cost-sensitive design requirements in IoT are dovetailing with national chip-sovereignty mandates, creating a strategic opening for vertically integrated players and regional champions across the RISC-V Tech market. Early commercialization of 128-bit cores, the arrival of ISO 26262- and ISO/SAE 21434-certified IP, and growing tool-chain standardization through the RVA23 Profile point to sustained scalability into high-performance computing, automotive, and industrial automation. Investors' willingness to deploy capital into open-hardware startups, as well as alliances that pool patents or link IP vendors with EDA suppliers, are further diluting the barriers to entry and accelerating convergence toward a more cohesive software and hardware stack.

Global RISC-V Tech Market Trends and Insights

Rapid proliferation of AI/ML-centric edge workloads

Edge AI adoption is lifting demand for modular processors able to tune latency and energy consumption, and the RISC-V Tech market is capitalizing on that pivot through vector extensions that accelerate neural-network inference in cameras, industrial sensors, and in-vehicle systems. Chinese semiconductor programs targeting indigenous AI chips have pressed home this advantage, minimizing vulnerability to Western export controls. The same open-standard flexibility is spawning a network of IP vendors, tool-chain developers, and certification bodies, compressing design cycles for domain-specific compute and helping to unlock new deployment models in automotive safety and factory automation.

Software tool-chain maturity attracting Tier-1 OEMs

Growing alignment around GCC, LLVM, and the RVA23 Profile has strengthened confidence in the RISC-V Tech market by offering unified toolchains and robust Java and Python runtimes. Flagship backers such as Intel, Google, and Nvidia are contributing code upstream, lowering switching costs and enabling Tier-1 OEMs to target multiple performance tiers under a single development workflow. As software stability improves, broad-based developers and ISVs have begun porting cloud, edge, and embedded stacks, moving the RISC-V Tech market deeper into enterprise and consumer segments.

Fragmented ISA extensions are increasing software complexity

Because the RISC-V specification permits custom extensions, dozens of vendors have introduced proprietary tweaks that complicate binary portability and continuous-integration pipelines. While the RVA23 Profile sets out mandatory AI/ML features, optional elements remain numerous, forcing OS vendors to maintain multiple kernels and tool-chain variants. Enterprise CIOs cite this as a reason to keep ARM-based roadmaps in parallel, delaying full commitment to the RISC-V Tech market.

Other drivers and restraints analyzed in the detailed report include:

- National chip-sovereignty programs (EU Chips Act, CHIPS and Science Act)

- Open-standard IP accelerating silicon time-to-market

- Limited backward-compatibility guarantees versus ARM ISA

For complete list of drivers and restraints, kindly check the Table Of Contents.

Segment Analysis

64-bit designs delivered 41.85% of the RISC-V Tech market share in 2025, translating into the largest slice of the RISC-V Tech market size. Semiconductor houses favor 64-bit cores because mainstream Linux distributions, Chromebook firmware, and containerized cloud software already support them, letting designers capture mass-market revenue without heavy re-engineering. Over the next three years, broader tool-chain maturity and big-core roadmaps such as SiFive's P870-D, which scales to 256 cores, will enable hyperscalers to test RISC-V racks at petascale performance levels.

The 128-bit cohort is registering a 58.2% CAGR, the fastest within the RISC-V Tech market, as exascale computing and AI models larger than 1 trillion parameters demand huge address spaces and high-precision vector math. Memory-intensive workloads in genomics and climate simulation are also nudging research centers to prototype 128-bit RISC-V clusters. Vendors are racing to add software support at the operating-system, hypervisor, and compiler levels, with early patches already appearing in GCC and LLVM. Although 32-bit cores remain the go-to choice for cost-sensitive IoT nodes, their share will compress modestly as more MCU vendors follow Renesas in migrating premium microcontrollers to 64-bit address spaces.

The RISC-V Tech Market Report is Segmented by Processor Core Type (32-Bit, 64-Bit, 128-Bit), Application (Smartphones, 5G Devices, Data Centers, and More), End-User Industry (Computing and Storage, Consumer Electronics, Medical, Industrial, and More), and Geography (North America, South America, Europe, Asia-Pacific, Middle East and Africa). The Market Forecasts are Provided in Terms of Value (USD).

Geography Analysis

Asia-Pacific retained 45.25% of 2025 revenue and will grow at a 62.7% CAGR through 2031 as state-led capital drives fab expansion, IP pooling, and verification labs. China's patent alliance reduces litigation hazards and empowers firms like Alibaba, T-Head, and Baidu to scale indigenous data-center and AI silicon. India's design-in-India campaigns are adding new assembly and test capacity, with Mindgrove planning volume MCU shipments in 2025.

Europe is carving an autonomy pathway through EUR 240 million in joint ventures such as DARE, eProcessor, and SiPearl's Rhea, engineered at the Barcelona Supercomputing Center. These programs leverage RISC-V to hedge geopolitical risk and promote supply-chain resilience, making the architecture a linchpin of EuroHPC's long-term road map. Focus areas include exascale HPC, energy-efficient edge nodes, and secure defense electronics.

North America remains the innovation crucible: new funding for Rivos, Tenstorrent, and other Silicon Valley startups underscores deep-tech investor confidence. CHIPS Act grants reinforce domestic prototyping capacity, while cross-border projects with Japanese partners accelerate 2 nm process adoption. Regional priorities include chiplets, low-power AI inference accelerators, and cloud-to-edge orchestration tools, all of which extend the reach of the RISC-V Tech market into high-performance segments where customization and license savings justify transition costs.

- Alibaba Group Holding Limited (T-Head Semiconductor)

- Andes Technology Corporation

- Antmicro Sp. z o.o.

- Apex Semiconductor (Shenzhen) Co., Ltd.

- Bluespec, Inc.

- C-Sky Microsystems Co., Ltd.

- CloudBEAR OU

- EMBEdded Logic Solutions Ltd.

- GreenWaves Technologies S.A.

- Huawei Technologies Co., Ltd. (HiSilicon)

- Imagination Technologies Limited

- Lattice Semiconductor Corporation

- Microchip Technology Incorporated

- MipSoC Ltd.

- Red Hat, Inc. (SiFive joint IP)

- Rivos Inc.

- SiFive, Inc.

- StarFive Technology Co., Ltd.

- Ventana Micro Systems, Inc.

- Western Digital Corporation

Additional Benefits:

- The market estimate (ME) sheet in Excel format

- 3 months of analyst support

TABLE OF CONTENTS

1 INTRODUCTION

- 1.1 Study Assumptions and Market Definition

- 1.2 Scope of the Study

2 RESEARCH METHODOLOGY

3 EXECUTIVE SUMMARY

4 MARKET LANDSCAPE

- 4.1 Market Overview

- 4.2 Market Drivers

- 4.2.1 Rapid proliferation of AI/ML-centric edge workloads

- 4.2.2 Software toolchain maturity attracting Tier-1 OEMs

- 4.2.3 National chip-sovereignty programs (EU Chips Act, CHIPS and Science Act)

- 4.2.4 Open-standard IP accelerating silicon time-to-market

- 4.2.5 Commercial-grade verification ecosystems (imperas, Synopsys partnerships)

- 4.2.6 Emergence of 3rd-party RISC-V accelerators for domain-specific compute

- 4.3 Market Restraints

- 4.3.1 Fragmented ISA extensions increasing software complexity

- 4.3.2 Limited backward-compatibility guarantees vs. ARM ISA

- 4.3.3 IP indemnification and patent-litigation uncertainties

- 4.3.4 Scarcity of RISC-V ready EDA talent in mature nodes

- 4.4 Industry Value Chain Analysis

- 4.5 Regulatory Landscape

- 4.6 Technological Outlook (Chiplet and Heterogenous Integration)

- 4.7 Impact of Macroeconomic Factors on the Market

- 4.8 Investment Analysis

- 4.9 Porter's Five Forces Analysis

- 4.9.1 Threat of New Entrants

- 4.9.2 Bargaining Power of Buyers

- 4.9.3 Bargaining Power of Suppliers

- 4.9.4 Threat of Substitute Products

- 4.9.5 Intensity of Competitive Rivalry

5 MARKET SIZE AND GROWTH FORECASTS (VALUE)

- 5.1 By Processor Core Type

- 5.1.1 32-bit

- 5.1.2 64-bit

- 5.1.3 128-bit

- 5.2 By Application

- 5.2.1 Smartphones

- 5.2.2 5G Devices

- 5.2.3 Data Centers

- 5.2.4 Personal Computers and Game Consoles

- 5.2.5 Cellular Network Infrastructure

- 5.2.6 IoT Devices

- 5.2.7 Other Applications

- 5.3 By End-User Industry

- 5.3.1 Computing and Storage

- 5.3.2 Communication Infrastructure

- 5.3.3 Consumer Electronics

- 5.3.4 Automotive and Transportation

- 5.3.5 Medical

- 5.3.6 Aerospace and Military

- 5.3.7 Industrial

- 5.3.8 Other End-User Industries

- 5.4 By Geography

- 5.4.1 North America

- 5.4.1.1 United States

- 5.4.1.2 Canada

- 5.4.1.3 Mexico

- 5.4.2 South America

- 5.4.2.1 Brazil

- 5.4.2.2 Argentina

- 5.4.2.3 Rest of South America

- 5.4.3 Europe

- 5.4.3.1 Germany

- 5.4.3.2 United Kingdom

- 5.4.3.3 France

- 5.4.3.4 Italy

- 5.4.3.5 Rest of Europe

- 5.4.4 Asia-Pacific

- 5.4.4.1 China

- 5.4.4.2 Japan

- 5.4.4.3 India

- 5.4.4.4 South-East Asia

- 5.4.4.5 Rest of Asia-Pacific

- 5.4.5 Middle East and Africa

- 5.4.5.1 Middle East

- 5.4.5.1.1 Saudi Arabia

- 5.4.5.1.2 United Arab Emirates

- 5.4.5.1.3 Rest of Middle East

- 5.4.5.2 Africa

- 5.4.5.2.1 South Africa

- 5.4.5.2.2 Egypt

- 5.4.5.2.3 Rest of Africa

- 5.4.5.1 Middle East

- 5.4.1 North America

6 COMPETITIVE LANDSCAPE

- 6.1 Market Concentration

- 6.2 Strategic Moves

- 6.3 Market Share Analysis

- 6.4 Company Profiles {(includes Global-level Overview, Market-level Overview, Core Segments, Financials as available, Strategic Information, Market Rank/Share for key companies, Products and Services, and Recent Developments)}

- 6.4.1 Alibaba Group Holding Limited (T-Head Semiconductor)

- 6.4.2 Andes Technology Corporation

- 6.4.3 Antmicro Sp. z o.o.

- 6.4.4 Apex Semiconductor (Shenzhen) Co., Ltd.

- 6.4.5 Bluespec, Inc.

- 6.4.6 C-Sky Microsystems Co., Ltd.

- 6.4.7 CloudBEAR OU

- 6.4.8 EMBEdded Logic Solutions Ltd.

- 6.4.9 GreenWaves Technologies S.A.

- 6.4.10 Huawei Technologies Co., Ltd. (HiSilicon)

- 6.4.11 Imagination Technologies Limited

- 6.4.12 Lattice Semiconductor Corporation

- 6.4.13 Microchip Technology Incorporated

- 6.4.14 MipSoC Ltd.

- 6.4.15 Red Hat, Inc. (SiFive joint IP)

- 6.4.16 Rivos Inc.

- 6.4.17 SiFive, Inc.

- 6.4.18 StarFive Technology Co., Ltd.

- 6.4.19 Ventana Micro Systems, Inc.

- 6.4.20 Western Digital Corporation

7 MARKET OPPORTUNITIES AND FUTURE OUTLOOK

- 7.1 White-space and Unmet-Need Assessment