PUBLISHER: Mordor Intelligence | PRODUCT CODE: 1937429

PUBLISHER: Mordor Intelligence | PRODUCT CODE: 1937429

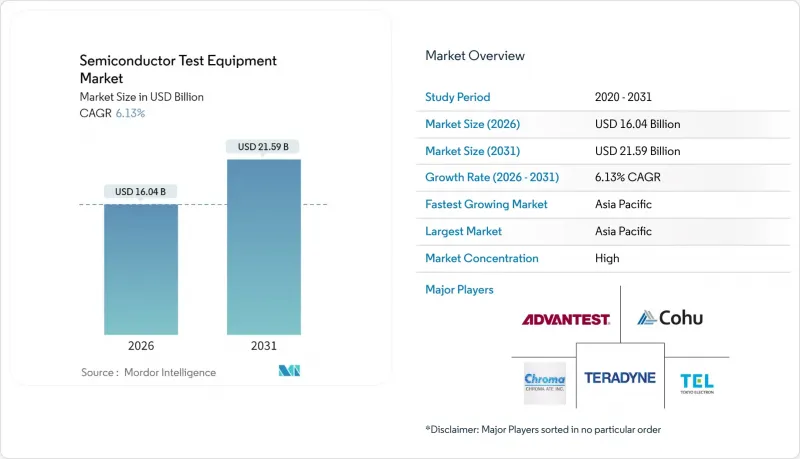

Semiconductor Test Equipment - Market Share Analysis, Industry Trends & Statistics, Growth Forecasts (2026 - 2031)

The semiconductor test equipment market was valued at USD 15.11 billion in 2025 and estimated to grow from USD 16.04 billion in 2026 to reach USD 21.59 billion by 2031, at a CAGR of 6.13% during the forecast period (2026-2031).

Demand acceleration reflects the rising complexity of AI processors, automotive electrification, and new packaging architectures that necessitate more precise validation. Rapid migration toward system-level testing, optical inspection, and adaptive analytics reshapes capital allocation as manufacturers pursue faster fault isolation and higher overall equipment effectiveness. The Asia-Pacific region anchors half of global revenue, yet North America and Europe are stepping up capacity under sovereignty programs that are widening regional demand for high-end testers. Competitive advantages shift toward suppliers that combine probe cards, analytics software, and application-specific expertise, while margin pressure persists because capital intensity grows faster than average selling prices. Strategic partnerships between ATE leaders and probe card specialists emphasize vertical integration as a hedge against supply chain fragility in critical mechanical interfaces.

Global Semiconductor Test Equipment Market Trends and Insights

Increasing AI/ML and Edge-Computing IC Volumes

Explosive uptake of generative AI creates unprecedented validation complexity that elevates automated testers equipped for very-high-pin-count devices. Order momentum for wafer-level burn-in and system-level suites reflects the semiconductor test equipment market pivot toward reliability screening under accelerated thermal stress profiles. AI accelerators integrate massive die areas and advanced memory stacks, prompting customers to invest in adaptive testers that synchronize with design-for-test hooks. Advantest reported new highs for revenue and profit in the first half of fiscal 2024 based on AI device demand, confirming that verification intensity is now a profit driver for suppliers rather than a cost center for chipmakers. The semiconductor test equipment industry responds by embedding machine-learning algorithms that cut dwell time without compromising coverage. Over the medium term, cloud service providers and hyperscale data-center operators will remain the dominant purchasers of ultra-high-throughput system-level testers.

Rapid Automotive Shift Toward ADAS and EV Platforms

Centralized vehicle compute architectures merge infotainment, battery management, and radar processing onto fusion chips whose functional safety must meet ISO 26262 requirements. This transition enlarges the test program scope from parametric checks to holistic scenario validation that mirrors on-road events. Keysight's certified toolchain underpins traceability from design to production, signaling how compliance criteria shape procurement in the semiconductor test equipment market. Reliability screening time for automotive-grade ICs stands nearly 2 times consumer-grade devices, fueling orders for burn-in ovens and power-aware handlers.

Increasing CAPEX Intensity Versus ASP Erosion

The semiconductor test equipment industry faces challenges as rising costs and declining prices impact profitability and limit investments in new technologies. SEMI reported global semiconductor equipment sales reached USD 113 billion in 2024, but margin compression persists as equipment complexity outpaces pricing power. Advanced packaging and chiplet architectures require specialized testing equipment, which comes at a higher cost, and face pricing pressure from customers as they protect their margins. KLA Corporation reported a 7% decline in revenue to USD 9.8 billion in fiscal 2024, driven by weaker market conditions in the semiconductor and wafer fabrication equipment sectors, highlighting the impact of pricing pressures. High-volume applications face added challenges as customers demand cost reductions alongside advanced testing capabilities. Manufacturers are focusing on automation, standardization, and research and development to maintain technological leadership.

Other drivers and restraints analyzed in the detailed report include:

- Expansion of 3D-IC and Advanced Packaging Capacity

- Mainstream Migration to Sub-5 nm Nodes

- Supply-Chain Fragility in Probe Cards and MEMS Sockets

For complete list of drivers and restraints, kindly check the Table Of Contents.

Segment Analysis

Automated test equipment retained 37.56% of the semiconductor test equipment market share in 2025, underscoring the category's entrenched position in volume production. The segment includes SoC, memory, and RF testers that now integrate AI-enabled diagnostics to accelerate pattern coverage. Advantest's T5801 validates GDDR7 and DDR6 devices, demonstrating that conventional testers are evolving to address the next-generation memory bandwidth requirements. Handler and probe equipment ensure thermal uniformity and precise alignment during parallel testing, lowering cost-per-site for high-pin-count devices.

Optical inspection systems are projected to record an 7.84% CAGR, the fastest within the semiconductor test equipment market, as chiplet and 3D packages introduce visual defects that traditional electrical checks miss. Infrared imaging, subsurface crack detection, and AI-assisted defect classification reshape quality control workflows. The semiconductor test equipment market size associated with optical solutions is expected to increase as fabs deploy them in both front-end and back-end lines. Partnerships between electrical and optical data will enable predictive analytics that cut rework rates and uplift first-pass yield.

The Semiconductor Test Equipment Market Report is Segmented by Product Type (Automated Test Equipment, Burn-In Systems, and More), Application (Wafer Sort/Probe, Final Test, System-Level Test, Reliability/Burn-in), End-Use Industry (Consumer Electronics, Automotive and Mobility, and More), and Geography (North America, South America, Europe, Asia-Pacific, and More). The Market Forecasts are Provided in Terms of Value (USD).

Geography Analysis

Asia-Pacific dominated the semiconductor test equipment market with a 49.62% share in 2025 and is on track for a 7.58% CAGR to 2031. Taiwan accelerates capex, with King Yuan Electronics allocating NTD 37 billion (USD 1.24 billion) to boost AI chip testing capacity, underscoring regional leadership. China deepens domestic tool development to offset export controls, while Southeast Asia's Malaysia and Singapore reinforce back-end specialization and silicon-photonics niches.

North America benefits from CHIPS Act incentives that funnel over USD 52 billion into new fabs, instigating parallel investment in testers and metrology. Intel's receipt of ASML's high-NA EUV tool signals volume ramp at sub-3 nm nodes, a catalyst for advanced ATE adoption. Europe pursues sovereignty through the EUR 10 billion (USD 11.65 billion) Dresden foundry joint venture, creating incremental demand for probe cards and system-level racks tailored to automotive clients. Germany's broader cluster, including planned Intel and Wolfspeed facilities, further diversifies regional tool consumption.

The Middle East and Africa remain nascent but show policy-driven interest in semiconductor self-sufficiency. Gulf Cooperation Council states finance design centers and talent pipelines that may evolve into localized testing hubs. Export-control tensions fragment global supply, pushing regions to secure critical interface components internally. The semiconductor test equipment market, therefore, adapts to a multipolar landscape in which supply-chain resiliency trumps pure cost optimization.

- Advantest Corporation

- Teradyne Inc.

- Cohu Inc.

- Chroma ATE Inc.

- Tokyo Electron Ltd.

- Tokyo Seimitsu Co. Ltd. (Accretech)

- National Instruments Corporation

- Astronics Corporation

- TESEC Corporation

- Hon Technology Co. Ltd.

- SPEA S.p.A.

- FormFactor Inc.

- MPI Corporation

- TSE Co. Ltd.

- Keysight Technologies Inc.

- Rohde & Schwarz GmbH & Co KG

- Test Research Inc. (TRI)

- MicroCraft Inc.

- SHIBAURA Mechatronics Corporation

- Sinfonia Technology Co. Ltd.

- UniTest Inc.

- Shenzhen RIGOL Technologies Co. Ltd.

- ChangChuan Technology Co. Ltd.

- YIK Corp.

- Bluechips Microhouse Co. Ltd.

Additional Benefits:

- The market estimate (ME) sheet in Excel format

- 3 months of analyst support

TABLE OF CONTENTS

1 INTRODUCTION

- 1.1 Study Assumptions and Market Definition

- 1.2 Scope of the Study

2 RESEARCH METHODOLOGY

3 EXECUTIVE SUMMARY

4 MARKET LANDSCAPE

- 4.1 Market Overview

- 4.2 Market Drivers

- 4.2.1 Increasing AI/ML and edge-computing IC volumes

- 4.2.2 Rapid automotive shift toward ADAS and EV platforms

- 4.2.3 Expansion of 3 D-IC and advanced packaging capacity

- 4.2.4 Mainstream migration to sub-5 nm nodes

- 4.2.5 Emergence of chiplet-based heterogeneous integration

- 4.2.6 In-line adaptive test analytics reducing OEE losses

- 4.3 Market Restraints

- 4.3.1 Increasing CAPEX intensity vs ASP erosion

- 4.3.2 Supply-chain fragility in probe cards and MEMS sockets

- 4.3.3 Talent crunch in RF test algorithm development

- 4.3.4 Escalating sustainability compliance costs

- 4.4 Industry Value Chain Analysis

- 4.5 Regulatory Landscape

- 4.6 Technological Outlook

- 4.7 Impact of Macroeconomic Factors on the Market

- 4.8 Porter's Five Forces Analysis

- 4.8.1 Threat of New Entrants

- 4.8.2 Bargaining Power of Buyers

- 4.8.3 Bargaining Power of Suppliers

- 4.8.4 Threat of Substitute Products

- 4.8.5 Intensity of Competitive Rivalry

5 MARKET SIZE AND GROWTH FORECASTS (VALUE)

- 5.1 By Product Type

- 5.1.1 Automated Test Equipment (ATE)

- 5.1.1.1 SoC Testers (System-on-Chip)

- 5.1.1.2 Memory Testers

- 5.1.1.3 RF Testers

- 5.1.1.4 Analog/Mixed-Signal Testers

- 5.1.1.5 Other Automated Test Equipments

- 5.1.2 Burn-in Systems

- 5.1.3 Handler Equipment

- 5.1.4 Probe Equipment

- 5.1.5 Optical Inspection Systems

- 5.1.6 Other Equipment Categories

- 5.1.1 Automated Test Equipment (ATE)

- 5.2 By Application

- 5.2.1 Wafer Sort / Probe

- 5.2.2 Final Test

- 5.2.3 System-Level Test

- 5.2.4 Reliability / Burn-in

- 5.3 By End-use Industry

- 5.3.1 Consumer Electronics

- 5.3.2 Automotive and Mobility

- 5.3.3 Industrial and Power

- 5.3.4 Telecommunications and Networking

- 5.3.5 Healthcare and Life-science

- 5.3.6 Other End-use Industries

- 5.4 By Geography

- 5.4.1 North America

- 5.4.1.1 United States

- 5.4.1.2 Canada

- 5.4.1.3 Mexico

- 5.4.2 South America

- 5.4.2.1 Brazil

- 5.4.2.2 Argentina

- 5.4.2.3 Rest of South America

- 5.4.3 Europe

- 5.4.3.1 Germany

- 5.4.3.2 United Kingdom

- 5.4.3.3 France

- 5.4.3.4 Russia

- 5.4.3.5 Rest of Europe

- 5.4.4 Asia-Pacific

- 5.4.4.1 China

- 5.4.4.2 Japan

- 5.4.4.3 India

- 5.4.4.4 South Korea

- 5.4.4.5 South-East Asia

- 5.4.4.6 Rest of Asia-Pacific

- 5.4.5 Middle East and Africa

- 5.4.5.1 Middle East

- 5.4.5.1.1 Saudi Arabia

- 5.4.5.1.2 United Arab Emirates

- 5.4.5.1.3 Rest of Middle East

- 5.4.5.2 Africa

- 5.4.5.2.1 South Africa

- 5.4.5.2.2 Egypt

- 5.4.5.2.3 Rest of Africa

- 5.4.5.1 Middle East

- 5.4.1 North America

6 COMPETITIVE LANDSCAPE

- 6.1 Market Concentration

- 6.2 Strategic Moves

- 6.3 Market Share Analysis

- 6.4 Company Profiles (includes Global level Overview, Market level overview, Core Segments, Financials as available, Strategic Information, Market Rank/Share for key companies, Products and Services, and Recent Developments)

- 6.4.1 Advantest Corporation

- 6.4.2 Teradyne Inc.

- 6.4.3 Cohu Inc.

- 6.4.4 Chroma ATE Inc.

- 6.4.5 Tokyo Electron Ltd.

- 6.4.6 Tokyo Seimitsu Co. Ltd. (Accretech)

- 6.4.7 National Instruments Corporation

- 6.4.8 Astronics Corporation

- 6.4.9 TESEC Corporation

- 6.4.10 Hon Technology Co. Ltd.

- 6.4.11 SPEA S.p.A.

- 6.4.12 FormFactor Inc.

- 6.4.13 MPI Corporation

- 6.4.14 TSE Co. Ltd.

- 6.4.15 Keysight Technologies Inc.

- 6.4.16 Rohde & Schwarz GmbH & Co KG

- 6.4.17 Test Research Inc. (TRI)

- 6.4.18 MicroCraft Inc.

- 6.4.19 SHIBAURA Mechatronics Corporation

- 6.4.20 Sinfonia Technology Co. Ltd.

- 6.4.21 UniTest Inc.

- 6.4.22 Shenzhen RIGOL Technologies Co. Ltd.

- 6.4.23 ChangChuan Technology Co. Ltd.

- 6.4.24 YIK Corp.

- 6.4.25 Bluechips Microhouse Co. Ltd.

7 MARKET OPPORTUNITIES AND FUTURE OUTLOOK

- 7.1 White-space and Unmet-need Assessment